# Advanced/RH LPX Motherboard Technical Product Specification

Order Number 281809-003 April 1996

THIS SPECIFICATION [DOCUMENT] IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. No other license, express or implied, by estoppel or otherwise, to any other intellectual property rights is granted herein. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to implementation of information in this specification. Intel does not warrant or represent that such implementation(s) will not infringe such rights.

A license is hereby granted to download a copy of this document for personal use only. This document is subject to change or update without notice.

Readers should not design products based on this document. Technical updates should be obtained by calling Intel Literature or writing:

Intel Corporation P.O. Box 7641 Mt. Prospect, II 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777,

Germany 44-0-1793-421-333, Japan (fax only) 81-0-120-478-832, other Countries 708-296-9333

Copyright © 1996, Intel Corporation

<sup>†</sup> Third-party brands and trademarks are the property of their respective owners.

# Advanced/RH Technical Product Specification

# Table of Contents

| Introduction                                         | 5        |

|------------------------------------------------------|----------|

| MOTHERBOARD MANUFACTURING OPTIONS                    | 6        |

| BOARD LEVEL FEATURES                                 | 7        |

| LPX FORM FACTOR                                      | 8        |

| CPU                                                  | 8        |

| PROCESSOR UPGRADE                                    | 9        |

| SECOND LEVEL CACHE                                   | 9        |

| SYSTEM MEMORY                                        | 9        |

| PERIPHERAL COMPONENT INTERCONNECT (PCI) PCISET       | 10       |

| NATIONAL SEMICONDUCTOR PC87306B SUPER I/O CONTROLLER | 11       |

| GRAPHICS SUBSYSTEM<br>AUDIO SUBSYSTEM                | 12<br>13 |

|                                                      | 13       |

| UNIVERSAL SERIAL BUS (USB)                           | 14       |

| Connectors                                           | 14       |

| MOTHERBOARD CONNECTORS                               | 14       |

| FRONT PANEL CONNECTIONS (J3A1, J2A1)                 | 16       |

| AUDIO CONNECTORS                                     | 18       |

| BACK PANEL CONNECTORS                                | 20       |

| Power Consumption                                    | 21       |

| Appendix A – User-Installable Upgrades               | 22       |

| SYSTEM MEMORY                                        | 22       |

| REAL TIME CLOCK BATTERY REPLACEMENT                  | 22       |

| CPU UPGRADE                                          | 22       |

| GRAPHICS MEMORY UPGRADE                              | 22       |

| HARDWARE MPEG MODULE                                 | 23       |

| Appendix B – Configuration Jumper Settings           | 24       |

| CPU CONFIGURATION - JUMPER BLOCK J4L1(C&D)           | 26       |

| CMOS -J4L1 A PINS 4-6                                | 26       |

| PSWD -J4L1 A PINS 1-3                                | 26       |

| SETUP - J4L1 B PINS 1-3                              | 26       |

| RISER - J4G1                                         | 26       |

| DRIVE OR OVERDRIVE - J6C2                            | 27       |

| RECOVERY JUMPER - J6C2                               | 27       |

| Appendix C – Memory Map                              | 28       |

| Appendix D – I/O Map                                 | 29       |

| Appendix E – PCI Configuration Space Map             | 30       |

| Appendix F – Interrupts & DMA Channels               | 31       |

| Appendix G – Connectors                           | 32 |

|---------------------------------------------------|----|

| POWER SUPPLY                                      | 32 |

| FRONT PANEL–J3A1                                  | 33 |

| BACK PANEL I/O                                    | 34 |

| PERIPHERALS                                       | 35 |

| MULTIMEDIA                                        | 36 |

| Appendix-H Motherboard BIOS                       | 39 |

| FLASH MEMORY IMPLEMENTATION                       | 39 |

| BIOS UPGRADES                                     | 39 |

| SETUP UTILITY                                     | 40 |

| PCI AUTO-CONFIGURATION                            | 40 |

| ISA PLUG 'N' PLAY                                 | 40 |

| ADVANCED POWER MANAGEMENT                         | 40 |

| LANGUAGE SUPPORT                                  | 41 |

| PCI IDE                                           | 41 |

| BOOT OPTIONS                                      | 41 |

| FLASH LOGO AREA                                   | 41 |

| SECURITY FEATURES                                 | 41 |

| Appendix I – PCI Configuration Error Messages     | 43 |

| Appendix J- AMIBIOS Error messages and Beep Codes | 44 |

| BEEP CODES                                        | 44 |

| ERROR MESSAGES                                    | 44 |

| ERROR MESSAGES (CONT.)                            | 45 |

| ISA NMI MESSAGES                                  | 45 |

| Appendix K – Soft-off Control                     | 46 |

| Appendix L – Environmental Standards              | 47 |

| MOTHERBOARD SPECIFICATIONS                        | 47 |

| Appendix M – Reliability Data                     | 48 |

# Introduction

The Advanced/RH motherboard integrates the latest advances in processor, memory, and I/O technologies into a standard LPX form factor that provides leading edge technology. This combination of high integration and high performance makes the Advanced/RH motherboard the ideal platform for the increasing requirements of today's (and tomorrow's) desktop applications in the corporate workspace.

The flexible LPX design will accept Pentium<sup>®</sup> processors operating at 75 MHz, 90 MHz, 100 MHz, 120 MHz, 133 MHz, 150 MHz and 166 MHz as well as future Pentium processors. The processor subsystem is complemented by a Revision 2.1 Card Edge Low Profile (CELP 2.1) socket that accepts either a 256 KB or 512 KB second level write-back cache module using pipelined synchronous burst technology. There is also an option for having 256 KB of Pipeline Burst SRAM soldered onto the motherboard. If cache memory is soldered on the motherboard, the CELP socket will not be installed. Only one type of cache may be used on the Advanced/RH motherboard. The memory subsystem is designed to support up to 512 MB of EDO DRAM (for improved performance) or standard Fast Page DRAM in standard 72-pin SIMM<sup>†</sup> sockets. A Type 7 Pentium OverDrive<sup>®</sup> socket provides an upgrade to future OverDrive processors.

The Advanced/RH motherboard utilizes Intel's 82430HX PCIset to provide increased integration and performance over other motherboard designs. The Intel 82430HX PCIset contains an integrated PCI Bus Mastering IDE controller with two high performance IDE interfaces for up to four IDE devices (such as hard drives, CD-ROM readers, and so forth). The 82430HX PCIset coupled with the integration of the industry's latest peripherals gives the user a robust computing platform.

Complementing the 82439HX PCI controller is the 82371SB PIIX3 ISA bridge, offering new technology like USB expandability. The PIIX3 performs as a host on the Universal Serial Bus, and in the middle of 1996 Advanced/RH will provide connectors to accommodate USB peripherals.

ATI<sup>†</sup> 264-VT video, with fast SGRAM video memory, provides excellent performance advantages over alternate solutions using EDO memory. ATI Media Connector modules, supplied by ATI Technologies, can be used to accelerate hardware MPEG and provide the tuner capabilities that previously required an entire add in card. Memory expansion modules, also supplied by ATI, can upgrade the motherboard from 1MB to 2 or 4 MB of SGRAM.

The National PC87306B Super I/O controller integrates the standard PC I/O functions: floppy interface, two FIFO serial ports, one EPP/ECP capable parallel port, a Real Time Clock, keyboard controller, and support for an IrDA<sup> $\dagger$ </sup> compatible infrared interface.

To provide for the increasing number of multimedia applications, a Creative<sup>†</sup> VIBRA16S audio CODEC is integrated onto the motherboard. Either consumer audio or business audio is selected by the OEM. Consumer audio will not have onboard jacks, like business audio, but will provide audio connections via an audio riser card. Either audio solution is provided by the VIBRA16S audio controller, and it provides 16-bit stereo, Sound Blaster Pro<sup>†</sup> compatible audio with full duplex capabilities to meet the demands of interactive multimedia applications. PCI and ISA expansion slots are supported by a connector on the motherboard designed to accept a riser card.

In addition to superior hardware capabilities, a full set of software drivers and utilities are available to allow advanced operating systems such as Microsoft<sup>†</sup> Windows<sup>†</sup> 95 to take full advantage of the hardware capabilities. Features such as bus mastering IDE, Windows 95-ready Plug 'N' Play, Advanced Power Management (APM) with application restart, software-controlled power supply shutdown, and full duplex audio are all provided by software available for the Advanced/RH.

# MOTHERBOARD MANUFACTURING OPTIONS

The following manufacturing options are available. Details for each option are found in the corresponding section of this specification.

#### AUDIO SUBSYSTEM

Business audio Consumer audio No audio

#### VIDEO SUBSYSTEM

ATI VT graphic controller ATI CT graphic controller

#### CACHE SUBSYSTEM

Soldered SRAM CELP socket

#### UNIVERSAL SERIAL BUS

USB No USB

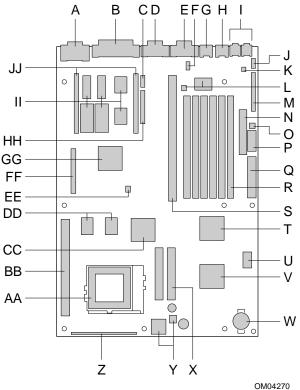

#### **BOARD LEVEL FEATURES**

- A VGA<sup>†</sup> connector

- B Parallel port connector

- C COM2 Header

- D COM2, or Dual in-line USB Connector

- E COM1 connector

- F- Four Pin CD-ROM audio connector

- G PS/2<sup>†</sup> Mouse port

- H PS/2 Keyboard port

- I Two 3.5 mm Audio Jacks (mic in, line out)

- J Eight Pin Wave table upgrade connector

- K 3 Pin Modem Audio Connector

- L Creative Labs Vibra 16S audio, Yamaha<sup>†</sup> OPL3 FM synthesizer

- M Midi Audio/Joystick connector

- N Floppy connector

- O Power Supply control connector

- P-3.3v Power connector

- Q Primary power connector

- R Six SIMM sockets (three banks)

- S PCI / ISA expansion connector

- T National PC87306B I/O controller

- U Flash BIOS

- V PCI ISA/IDE Xcelerator (PIIX3)

- W Battery for the Real-time clock

- X Two PCI IDE interfaces

- Y CPU 3.3v voltage regulator

- Z Front Panel I/O connector

- AA Socket 7 Pentium Processor socket

- BB Celp 2.1 connector cache module socket

- CC 82439HX controller (TXC)

- DD 256K L2 PBSRAM

- EE Riser Card 2/3 slot jumper

- FF ATI Media Channel Connector for H/W MPEG

- GG ATI graphics controller

- HH Configuration jumper blocks

- II Up to 2 MB graphics memory

- JJ SGRAM Graphics memory upgrade header

(This figure identifies the location of motherboard manufacturing options. Not all locations will be populated on all motherboards.)

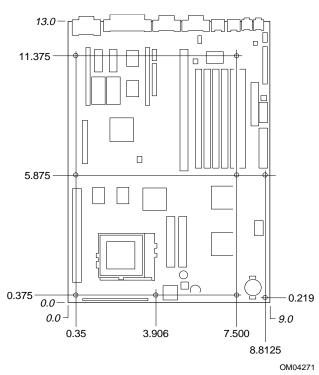

# LPX FORM FACTOR

The Advanced/RH motherboard is designed to fit into a standard LPX form factor chassis. Figure 2 illustrates the mechanical form factor for the Advanced/RH. The Advanced/RH LPX form factor does adhere to the standard LPX guidelines in that the outer dimensions are 13" x 9". Location of the I/O connectors, riser slot, and mounting holes are in strict compliance with the LPX specification. However, if business audio is selected by an OEM, a slight modification to the OEM's chassis may be necessary to accept the audio jacks on the motherboard.

Figure 2. Advanced/RH Motherboard dimensions

#### CPU

The Advanced/RH LPX motherboard is designed to operate with 3.3 volt Pentium processors. The 3.3 volt power is provided by a patented on-board voltage regulator circuit. An on-board jumper enables use of VRE specified processors. The voltage regulator provides the required voltage for the processor from the 5 volt output of a standard power supply. Processors which run internally at 75, 90, 100, 120, 133, 150 and 166 MHz, and have iCOMP<sup>®</sup> ratings of 615, 735, 815, 1000, 1110, 1176 and 1308 respectively are supported. Future Pentium processors will also be supported.

The Pentium processor maintains full backward compatibility with the 8086, 80286, Intel386<sup>™</sup> and Intel486<sup>™</sup> processors. It supports both read and write burst mode bus cycles, and includes separate 8 KB on-chip code and data write-back caches. Also integrated into the Pentium processor is an advanced numeric coprocessor which significantly increases the speed of floating point operations, while maintaining backward compatibility with the Intel486DX<sup>™</sup> math coprocessor and complying to ANSI/IEEE standard 754-1985.

# PROCESSOR UPGRADE

The Advanced/RH motherboard is manufactured with the 321-pin (socket 7) ZIF processor socket. Socket 7 provides a processor upgrade path that includes higher performance Pentium OverDrive processors than can be supported with socket 5. The motherboard is built to support uniplane CPUs. However, a manufacturing option allows the socket 7 design to support split voltage planes that can supply different voltages for a processor's CPU core and for the I/O core. Installing a split plane CPU into a motherboard configured only for uniplane processor may cause damage to the CPU.

# SECOND LEVEL CACHE

The Intel 82430HX PCIset supports a second level cache that uses high performance Synchronous Pipeline Burst SRAM. Asynchronous cache is not supported by the 82430HX controller. Pipeline Burst (PB) SRAM provides performance similar to expensive Synchronous Burst SRAMs for only a slight cost premium over slower performing asynchronous SRAMs.

As a manufacturing option, the Advanced/RH motherboard without onboard cache can be provided with a Card Edge Low Profile (CELP) version 2.1 socket that provides flexibility for second level cache options. The CELP socket can accommodate either a 256 KB or 512 KB cache module and is designed to work with modules that adhere to the COAST (Cache On A Stick) specification, version 2.1. The cache size is automatically detected and configured by the system BIOS for optimal performance. For a list of cache module suppliers or a copy of the COAST specification, contact your local Intel sales office or Intel authorized distributor.

#### SYSTEM MEMORY

The Advanced/RH motherboard provides six 72-pin SIMM sites for memory expansion. The sockets support 512 KB x 32 (2MB double sided SIMMs only), 1M x 32 (4 MB), 2M x 32 (8 MB), 4M x 32 (16 MB), 8M x 32 (32 MB), 16M x 32 (64MB), and 32M x 32 (128MB) single-sided or double-sided SIMM modules. Minimum memory size is 8 MB and maximum memory size, using four 32M x 32 SIMM modules, is 512 MB. Memory timing requires 70 ns fast page devices or, for optimum performance 60 ns EDO DRAM. 36-bit SIMM modules may be used for parity or ECC generation and checking.

The six sockets are arranged as Bank 0, Bank 1, and Bank 2. Each bank consists of two sockets and provides a 64/72-bit wide data path. Both SIMMs in a bank must be of the same memory size and type, although each bank may have different types of memory installed. It is even possible to have 70 ns Fast Page DRAM in one bank and 60 ns EDO DRAM in the other, in which case each bank is independently optimized for maximum performance. Any combination of the banks may be populated. There are no jumper settings required for the memory size or type, which is automatically detected by the system BIOS. The Advanced/RH motherboard supports only tin-lead SIMMs.

When banks 1 and 2 are populated at the same time, memory timing is modified from x333 to x444. This is due to loading on the address line shared by these two banks. In most applications the L2 cache will mask any performance degradation that is incurred. In addition, when using EDO Parity memory in an ECC configuration memory timing is changed from x222 to x333 to allow the chipset to perform Read Modify Writes.

#### EDO DRAM

Extended Data Out, or Hyper Page, DRAM is designed to improve the DRAM read performance. EDO DRAM holds the memory data valid until the next CAS# falling edge, unlike standard fast page mode DRAM which tri-states the memory data when CAS# negates to precharge for the next cycle. With EDO, the CAS# precharge overlaps the data valid time, allowing CAS# to negate earlier while still satisfying the memory data valid window time.

# EXPANSION RISER

An expansion slot riser connector of EISA form factor provides the capability to support either two or three PCI slots by changing a motherboard jumper to route any extra IRQ and ID selects. A riser board can also support up to five ISA expansion slots. The PCI bus is compliant with the PCI 2.1 specification.

To ensure that the lowest positioned slot on the riser card can support a full length add-in card the following conditions must be met.

- 1) The minimum height requirement for the lowest positioned slot on the CPU side of the riser is 1.2". Therefore the CPU heat sink should be no more than 1.2" high once installed on the processor.

- 2) The minimum height requirement for the lowest positioned slot on the SIMM side of the riser is 1.3". Therefore, once SIMM memory is installed they should not be taller than 1.3".

#### PERIPHERAL COMPONENT INTERCONNECT (PCI) PCISET

The Intel 82430HX PCIset is made up of two components: The 82439HX controller (TXC) and the 82371SB PCI ISA IDE Xcellerator (PIIX3) ISA bridge. The PCIset provides the following functions:

- CPU interface control

- Integrated L2 write-back cache controller – Pipeline Burst SRAM

- $-\,256~\text{KB}$  or 512 KB Direct Mapped

- Integrated DRAM controller

- 64/72-bit path to Memory

- Support for EDO and Fast Page DRAM

- 8 MB to 512 MB main memory

- Parity and ECC support

- Fully synchronous PCI bus interface

25/30/33 MHz

PCI to DRAM > 100 Mbytes/sec

- PCI to DRAM > 100 Mbytes/sec

Interface between the PCI bus and ISA bus

- Interface between the PCI bus and ISA b

Universal Serial Bus Controller

- (with B0 stepping of the PIIX 3)

- Host/Hub Controller

- Two USB ports

- Integrated fast IDE interface

- Support for up to 4 devices

- $-\operatorname{PIO}$  Mode 4 transfers up to 16 MB/sec

- Integrated 8 x 32-bit buffer for Bus Master PCI IDE burst transfers

- Bus Master mode

- PCI 2.1 Compliant

- Enhanced Fast DMA controller

- Interrupt controller and steering

- Counters/Timers

- SMI interrupt logic and timer with Fast On/Off mode

#### 82439HX TXC

The 439HX controller provides all control signals necessary to drive a second level cache and the DRAM array, including multiplexed address signals. It also controls system access to memory and generates snoop controls to maintain cache coherency. The 439HX controller comes in a 324 pin Ball Grid Array package.

#### 82371SB PCI ISA IDE XCELERATOR (PIIX3)

The PIIX3 provides the interface between the PCI and ISA buses and integrates a dual channel fast IDE interface capable of supporting up to 4 devices. USB host/hub bus is provided by the PIIX 3. The PIIX3 integrates seven 32-bit DMA channels, five 16-bit timer/counters, two eight-channel interrupt controllers, PCI-to-AT interrupt mapping circuitry, NMI logic, ISA refresh address generation, and PCI/ISA bus arbitration circuitry onto the same device. The PIIX3 comes in a 208 pin QFP package.

# IDE SUPPORT

The Advanced/RH motherboard provides two independent high performance bus-mastering PCI IDE interfaces capable of supporting PIO Mode 3 and Mode 4 devices. The system BIOS supports Cylinder Sector Head (CHS), Logical Block Addressing (LBA) and Extended Cylinder Sector Head (ECHS) translation modes as well as ATAPI (e.g. CD-ROM) devices on both IDE interfaces. IDE device transfer rate and translation mode capability can be automatically determined by the system BIOS.

Normally, programmed I/O operations require a substantial amount of CPU bandwidth. In multi-tasking operating systems like Microsoft Windows 95, the CPU bandwidth freed up by using bus mastering IDE can be used to complete other tasks while disk transfers are occurring. A driver is required for the IDE interface to operate as a PCI bus master capable of supporting PIO Mode 4 devices with transfer rates up to 22 MB/sec while minimizing the system demands upon the processor.

Detailed information on the PCIset is available in the Intel 82430HX PCIset data sheet.

#### NATIONAL SEMICONDUCTOR PC87306B SUPER I/O CONTROLLER

Control for the integrated serial ports, parallel port, floppy drive, RTC and keyboard controller is incorporated into a single component, the National Semiconductor PC87306B. This component provides:

- Two NS16C550-compatible UARTs with send/receive 16 byte FIFO

- Support for an IrDA compliant Infra Red interface

- Multi-mode bi-directional parallel port

- Standard mode; IBM<sup>†</sup> and Centronics<sup>†</sup> compatible

- Enhanced Parallel Port (EPP) with BIOS/Driver support

- High Speed mode; Extended Capabilities Port (ECP) compatible

- Industry standard floppy controller with 16 byte data FIFO (2.88 MB floppy support)

- Integrated Real Time Clock accurate within +/- 13 minutes/yr at 25° C and 5 volts when the system is continuously powered on

- Integrated 8042 compatible keyboard controller

The PC87306B is normally configured by the BIOS automatically. However configuration of these interfaces is possible via the CMOS Setup program that can be invoked during boot-up. The serial ports can be enabled as COM1, COM2, IrDA, or disabled. The parallel port can be configured as normal, extended, EPP/ECP, or disabled. The floppy interface can be configured for 360 KB or 1.2 MB 5<sup>1</sup>/<sub>4</sub>" media or for 720 KB, 1.2 MB, 1.44 MB, or 2.88 MB 3<sup>1</sup>/<sub>2</sub>" media. Header pins located near the back of the board allow cabling to use these interfaces

#### FLOPPY CONTROLLER

The PC87306B is software compatible with the DP8473 and 82077 floppy disk controllers. The floppy interface can be configured for 360 KB or 1.2 MB 5<sup>1</sup>/<sub>4</sub>" media or for 720 KB, 1.2 MB, 1.44 MB, or 2.88 MB 3<sup>1</sup>/<sub>2</sub>" media in the BIOS setup. By default, the Floppy A interface is configured for 1.44 MB and Floppy B is disabled. Another setup option prevents the user from being able to write to floppy. Configuring the floppy interface for 1.2 MB 3 <sup>1</sup>/<sub>2</sub>" (3-mode floppy) requires the use of a driver to operate correctly.

#### KEYBOARD INTERFACE

PS/2 keyboard/mouse connectors are located on the back panel side of the motherboard. The 5V lines to these connectors are protected with a PolySwitch<sup>†</sup> circuit which acts much like a self-healing fuse, re-establishing the connection after an over-current condition is removed. While this device eliminates the possibility of having to replace a fuse, care should be taken to turn off the system power before installing or removing a keyboard or mouse. The system BIOS can detect and correct keyboards and mice plugged into the wrong  $PS/2^{\dagger}$  style connector.

The integrated 8042 microcontroller contains the AMI Megakey keyboard/mouse controller code which, besides providing traditional keyboard and mouse control functions, supports Power-On/Reset (POR) password protection. The POR password can be defined by the user via the Setup program. The keyboard controller also provides for the following "hot key" sequences:

- <CTRL><ALT><DEL>: System software reset. This sequence performs a software reset of the system by jumping to the beginning of the BIOS code and running the POST operation.

- <CTRL><ALT><+> and <CTRL><ALT><->: Turbo mode selection. <CTRL><ALT><-> sets the system for deturbo mode, emulating an 25 MHz AT, and <CTRL><ALT><+> sets the system for turbo mode. Changing the Turbo mode may be prohibited by an operating system, or when the CPU is in Protected mode or virtual x86 mode under DOS.

- <CTRL><ALT><defined in setup>: Power down and coffee-break key sequences take advantage of the SMM features of the Pentium Processor to greatly reduce the system's power consumption while maintaining the responsiveness necessary to service external interrupts.

# REAL TIME CLOCK, CMOS RAM AND BATTERY

The integrated Real Time Clock (RTC) is DS1287 and MC146818 compatible and provides a time of day clock and a 100-year calendar with alarm features. The RTC can be set via the BIOS SETUP program. The RTC also supports a 242-byte battery-backed CMOS RAM area in two banks. This area is reserved for BIOS use. The CMOS RAM can be set to specific values or cleared to the system default values using the BIOS SETUP program. Also, the CMOS RAM values can be cleared to the system defaults by using a configuration jumper on the motherboard. Table B-1, in Appendix B, lists the configuration jumper settings.

An external coin-cell style battery provides power to the RTC and CMOS memory. The battery has an estimated lifetime of three years if the system is not plugged into the wall socket. When the system is plugged in, power is supplied from the LPX power supply's 5v standby current to extend the life of the battery. See Appendix A for information regarding replacement batteries.

#### IRDA (INFRA-RED) SUPPORT

A 5-pin interface on the front panel I/O connector is provided to allow connection to a Hewlett Packard HSDSL-1000 compatible Infra-red (IrDA) transmitter/receiver. Once the module is connected to the front panel I/O header, serial port 2 can be re-directed to the IrDA module, allowing the user to transfer files to or from portable devices such as laptops, PDA's and printers using application software such as LapLink. The IrDA specification provides for data transfers at 115 Kbps from a distance of 1 meter.

#### PARALLEL PORT

The Parallel port can be configured in the BIOS setup as output only compatible mode, bi-directional mode, ECP or EPP modes. The highly flexible parallel port can also be assigned to I/O addresses 278H, 378H, or 3BCH and IRQ's 5 or 7. Furthermore, a routable DMA scheme allows Plug 'N' Play operating systems such as Windows 95 to route either DMA channel 1 or 3 to the parallel port for ECP mode. EPP BIOS support must be provided by a device driver or TSR.

# **GRAPHICS SUBSYSTEM**

The ATI-264VT controller is a highly integrated multimedia graphics & video controller for PCI bus systems. The VT achieves enhanced performance with an all in one design that integrates a video scaler, a color space converter, a true color palette DAC, and a triple clock synthesizer with ATI's proven Mach64<sup>†</sup> graphics engine. The ATI-264VT controller is register compatible with ATI's Mach64 accelerator series, and therefore is immediately compatible with a wide range of software applications and drivers.

As a manufacturing option, the Advanced/RH board is also available with an ATI-264CT video controller and 1 MB of EDO video DRAM, upgradeable to a total of 2 MB by adding 1 MB of socketed video DRAM.

# ATI-264VT RESOLUTIONS SUPPORTED BY THE MOTHERBOARD

| Resolution     | 1 MB<br>SGRAM | 2 MB<br>SGRAM | Max Vertical<br>Refresh Rate |

|----------------|---------------|---------------|------------------------------|

| 640x480x4bpp   | Х             | Х             | 100 Hz                       |

| 640x480x8bpp   | Х             | Х             | 100 Hz                       |

| 640x480x16bpp  | Х             | Х             | 100 Hz                       |

| 640x480x24bpp  | Х             | Х             | 100 Hz                       |

| 640x480x32bpp  |               | Х             | 60 Hz                        |

| 800x600x4bpp   | Х             | Х             | 100 Hz                       |

| 800x600x8bpp   | Х             | Х             | 100 Hz                       |

| 800x600x16bpp  | Х             | Х             | 100 Hz                       |

| 800x600x24bpp  |               | Х             | 100 Hz                       |

| 1024x768x4bpp  | Х             | Х             | 100 Hz                       |

| 1024x768x8bpp  | Х             | Х             | 100 Hz                       |

| 1024x768x16bpp |               | Х             | 100 Hz                       |

| 1280x1024x4bpp | Х             | Х             | 75 Hz                        |

| 1280x1024x8bpp |               | Х             | 75 Hz                        |

Table 1. Advanced/RH Audio resource mapping

# GRAPHICS DRIVERS AND UTILITIES

Graphics drivers and utilities for Windows<sup> $\dagger$ </sup> 3.11 or for Windows 95 are supplied with the Advanced/RH motherboard.

# AUDIO SUBSYSTEM

The Advanced/RH offers three audio options for the OEM. The consumer audio option uses an onboard header to route audio to a riser card in the I/O panel. Consumer audio also includes a wave table upgrade header for future expansion.

The business audio option includes mike and line jacks on the motherboard next to the mouse and keyboard connectors. A third option is to have the board with no on-board audio.

The Advanced/RH audio subsystem is based upon the Creative Labs Vibra 16S audio controller and Yamaha OPL3 FM synthesizer. The controller features a 16-bit stereo audio sub-system as a factory installed option along with the OPL3 FM synthesizer. The Vibra 16S controller provides all the digital audio and analog mixing functions required for recording and playing of audio on personal computers. These functions include stereo analog-to-digital and digital-to-analog converters, analog mixing, anti-aliasing and reconstruction filters, line and microphone level inputs, and digital audio compression via selectable A-law / µlaw, and full digital control of all mixer and volume control functions.

# VIBRA 16S RESOURCE MAP

| Base Address (software configured)    | Joystick Enable (software configured)    |  |

|---------------------------------------|------------------------------------------|--|

| 220H - 22FH(Default) or               | Default Enabled                          |  |

| 240H - 24FH or                        | Interrupt (Software configured)          |  |

| 260H - 26FH or                        | IRQ2/9 or                                |  |

| 280H - 28FH                           | IRQ5 (default) or                        |  |

| FM Address (fixed)                    | IRQ7 or                                  |  |

| 388H - 38BH                           | IRQ10                                    |  |

| Joystick Address/Game Port (fixed)    | 8-bit DMA Channel (software configured)  |  |

| 200H - 207H                           | DMA Channel 1 (default) or               |  |

| MPU-401 Address (software configured) | DMA Channel 3                            |  |

| 300H - 301H or                        | 16-bit DMA Channel (software configured) |  |

| 330H - 331H (default)                 | DMA channel 5 (default)                  |  |

| MPU-401 Enable (software configured)  | DMA channel 7                            |  |

| Default is disabled                   |                                          |  |

# AUDIO DRIVERS

Audio software and utilities are provided for the Advanced/RH motherboard. A Windows setup program installs all of the software programs and utilities onto the system hard drive. Included in the Creative audio software are DOS utilities that allow the user to play a CD-ROM, control sound volume and mixer settings, run diagnostics, and switch between Sound Blaster Pro and Windows Sound System modes. Windows drivers and utilities include the Windows sound driver, audio input control panel, audio mixer control panel, and a business audio transport utility.

# UNIVERSAL SERIAL BUS (USB)

When B0 steppings of PIIX 3 are used in manufacturing, USB connectors may be added as a manufacturing option to support the new technology. The USB connector will occupy the serial 2 connector location, and there is a header to reroute COM2 to a breakout in the chassis or IO panel if the customer so desires.

# Connectors

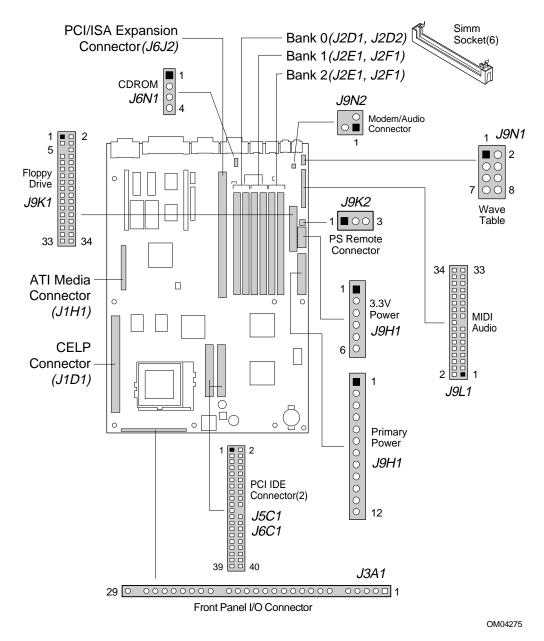

#### **MOTHERBOARD CONNECTORS**

There are connectors on-board for Floppy, IDE, Graphics memory upgrade sockets, VESA<sup> $\dagger$ </sup> feature connector, SIMMs, CELP cache modules, battery holder and front panel I/O connectors.

Figure 3. Advanced/RH connector locations

# POWER SUPPLY CONTROL (J9H1, J9K2)

When used with a power supply that supports remote power on/off, the Advanced/RH motherboard can turn off the system power via software control ("soft-off"). The Powerman utility supplied for Windows 3.1x allows for soft-off as does the shutdown icon in Windows 95 Start menu. The system BIOS will turn the system power off when it receives the proper APM command from the OS. For example, Windows 95 will issue this APM command when the user selects the "Shutdown the computer" option. Note that APM must be enabled in the system BIOS and OS in order for the soft-off feature to work correctly. Power supplies that support "soft-off" connect to the motherboard via the 3-pin "PWS CNTRL" connector, which is a Molex 2695 connector featuring a security latch for reliability. In order for the system to recognize the presence of a "soft-off" power supply, the supply must tie pin 3 of the PWS Control connector to ground.

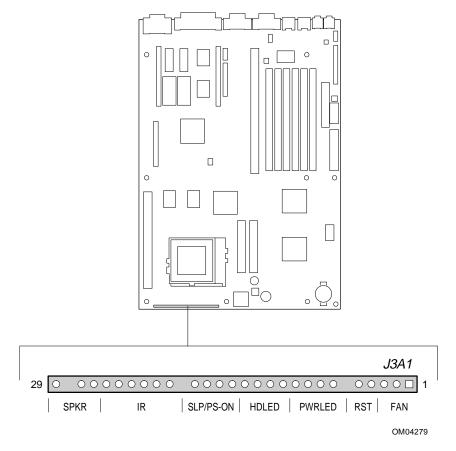

# FRONT PANEL CONNECTIONS (J3A1, J2A1)

The Advanced/RH motherboard provides header connectors to support functions typically located on the chassis bezel. Refer to Appendix G for exact pinout definitions for all of the connectors. Front panel features supported include:

- System Speaker

- Infra-Red (IrDA) port

- Sleep/Resume

- Hard Drive activity LED

- Power LED

- System Reset

- CPU fan

Figure 4. Front Panel I/O Connectors

#### SPEAKER

The external speaker provides error beep code information during the Power-On Self Test if the system cannot use the video interface. If no speakers are plugged into the audio output jack, the audio output is redirected to the external PC speaker.

#### SLEEP / RESUME

When Advanced Power Management (APM) is activated in the system BIOS and the operating system's APM driver is loaded, Sleep mode (Stand-By) can be entered in one of three ways: an optional front panel "Sleep/Resume" button, a user defined keyboard hot key, or prolonged system inactivity. The Sleep/Resume button is supported by a 2-pin header located on the front panel I/O connector. Closing the "Sleep" switch will generate an SMI (System Management Interrupt) to the processor which immediately goes into System Management Mode (SMM), the so called "Sleep" mode. The front panel "Sleep mode" switch must be a momentary two pin SPST type that is normally open. The function of the Sleep/Resume button can also be achieved via a keyboard hot-key sequence, or by a time-out of the system inactivity timer. Both the keyboard hot-key and the inactivity timer are programmable in the BIOS setup (timer is set to 10 minutes by default). To re-activate the system, or "Resume", the user must simply press the sleep/resume button again, or use the keyboard or mouse. Note that mouse activity will only "wake up" the system if a mouse driver is loaded. While the system is in Stand-By or "sleep" mode it is fully capable of responding to and servicing external interrupts (such as incoming fax) even though the monitor will only turn on if a user interrupt (keyboard/mouse) occurs as mentioned above. This interface is also supported by pins 1 and 2 of the PS SLEEP connector.

#### INFRA-RED (IRDA) CONNECTOR

Serial port 2 can be configured to support an IrDA module via a 5 pin header connector. Once configured for IrDA, the user can transfer files to or from portable devices such as laptop computers, PDA's or printers using application software such as Traveling Software's LapLink. The IrDA specification provides for data transfers at 115 Kbps from a distance of 1 meter.

#### RESET

This 2-pin header can be connected to a momentary SPST type switch that is normally open. When the switch is closed, the system will hard reset and run POST.

#### AUDIO CONNECTORS

There are two methods of accessing the audio features on the Advanced/RH. The method installed depends on the audio option that has been selected. For business audio, audio is accessed using audio jacks provided on the motherboard. These two 1/8" jacks supply Line Out, and Mic In connections and are available through the back I/O panel.

#### MIDI/AUDIO I/O CONNECTOR

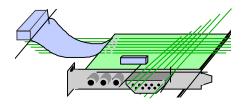

Consumer audio is provided by using an audio riser card connected to the audio/midi connector of the motherboard. The audio riser card contains all of the necessary audio jacks (Speaker Out, Line In, Mic In) and the game port. It plugs into a 34-pin header connector on the motherboard. An example of the consumer audio riser card is shown below. The audio connectors are 1/8" stereo jacks

Figure 5. Advanced/RH Consumer audio I/O module

#### CD-ROM AUDIO INPUT

A four pin connector is provided for interfacing the audio output stream from a CD-ROM reader into the audio sub-system mixer. This connector is compatible with the typical cable that is supplied with CD-ROM readers for interfacing to audio add-in cards. This feature is available in both consumer and business audio options.

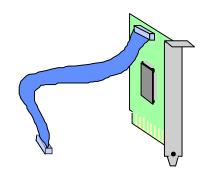

# WAVE TABLE UPGRADE

An eight pin header is provided as part of the consumer audio option to connect to a wave table upgrade card for richer sound quality in both DOS and Windows environments. The wave table upgrade module is simply installed into a standard ISA slot with a cable routed to the connector.

Compatible wave table upgrade cards are available from several venders; the ICS WaveFront upgrade module and the CrystaLake Series 2000 wave table product family add a complete General MIDI compatible music solution to the Advanced/RH based system.

For more information on CrystaLake products Contact CrystaLake Mulitmedia at http://www.teleport.com/~crystal, or (503) 222-2603 ext. 209

Figure 6. Advanced/RH Wave Table Upgrade module

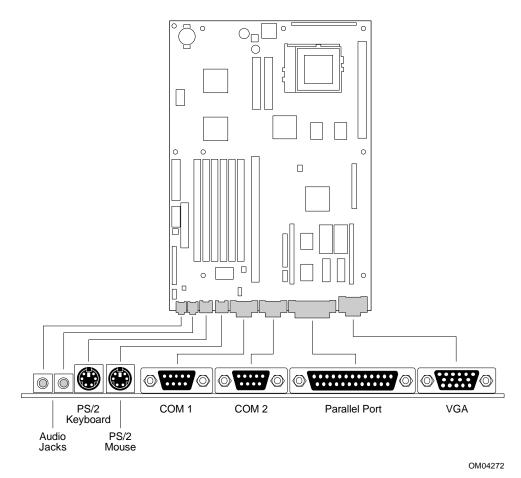

# BACK PANEL CONNECTORS

The back panel provides external access to PS/2 style keyboard and mouse connectors as well as two serial and one parallel port, which are integrated on the Advanced/RH motherboard. If a USB connector is present, COM2 can be routed to a back panel knockout from the COM2 header on the motherboard. Audio jacks for Speaker Out and Microphone are provided for business audio on the back I/O panel. By adding an audio riser for consumer audio solutions a Midi/Game port can be made available through an ISA panel. Figure 5 shows the general location of the I/O connectors. Business audio jacks and the consumer audio/midi riser are mutually exclusive features.

Figure 7. Back Panel I/O Connectors

# **Power Consumption**

Tables 3 and 4 list the measured current and voltage requirements for the Advanced/RH motherboard configured with 16 MB of DRAM. Table 5 lists the typical power consumed by the same configuration. This information is preliminary and is provided only as a guide for calculating approximate total system power usage with additional resources added.

#### Voltage

| DC Voltage        | Acceptable tolerance |

|-------------------|----------------------|

| +3.3V             | +/- 5%               |

| +5V               | +/- 5%               |

| +5V SB (stand by) | +/- 5%               |

| -5V               | +/- 5%               |

| +12V              | +/- 5%               |

| -12V              | +/- 5%               |

Table 3. Advanced/RH Voltage tolerance

#### **Current and Power**

|                     | AC (watts) | DC (amps) |       |  |

|---------------------|------------|-----------|-------|--|

|                     |            | +5v       | +12v  |  |

| No APM enabled      |            |           |       |  |

| DOS prompt          | 28         | 3.5A      | 160mA |  |

| Windows95 @1024x768 | 28         | 4.0A      | 160mA |  |

| APM enabled         |            |           |       |  |

| DOS prompt          | 24.3       | 2.2A      | 160mA |  |

| Windows95 @1024x768 | 24.4       | 2.2A      | 160mA |  |

| Suspended           | 20.3       | 2.2A      | 160mA |  |

Table 4. Advanced/RH Power and Current Requirements

#### **System Configuration**

System Configuration Advanced/RH motherboard, 166 MHz Pentium Processor, 24 MB EDO RAM, 256 KB PBSRAM L2 cache, Floppy drive, 1.6 GB hard drive, Sony CDU-77E CD-ROM drive

Table 5. Power use by System Resources

# Appendix A – User-Installable Upgrades

| Supported SIMM Sizes                                  | Bank Size                      | Note |

|-------------------------------------------------------|--------------------------------|------|

| 512K x 32 (2 MB)                                      | 4MB                            | 1    |

| 1M x 32 (4 MB)                                        | 8MB                            |      |

| 2M x 32 (8 MB)                                        | 16MB                           |      |

| 4M x 32 (16 MB)                                       | 32MB                           |      |

| 8M x 32 (32 MB)                                       | 64MB                           | 2    |

| 16M x 32 (64MB)                                       | 128MB                          | 2    |

| 32M x 32 (128MB)                                      | 256MB                          | 2    |

| 4M x 32 (16 MB)<br>8M x 32 (32 MB)<br>16M x 32 (64MB) | 32MB<br>64MB<br>128MB<br>256MB | 2    |

# SYSTEM MEMORY

Table A-1. Supported Memory SIMM Sizes and Configuration

Note 1: 512K x 32 SIMMs are supported, however, they must be double sided SIMMs

Note: 2 When using Single Sided High Density SIMMs such as 32 MB single sided, 64 MB double sided, or 128 MB SIMMs, SIMMs that have less than 32 MB per side will NOT be recognized in the system.

The Advanced/RH will support both Fast Page DRAM or EDO DRAM SIMMs, but they cannot be mixed within the same memory bank. If Fast Page DRAM and EDO DRAM SIMMs are installed in separate banks, each bank will be optimized for maximum performance. Parity or ECC generation and detection are supported when parity SIMMs are the only SIMMs present on the motherboard. SIMM requirements are 70 ns Fast Page Mode or 60 ns EDO DRAM with tin-lead connectors.

8 MB is the minimum memory size supported by the Advanced/RH motherboard. 512 MB is the maximum memory that can be supported in any combination of SIMMs from the table.

# REAL TIME CLOCK BATTERY REPLACEMENT

The battery can be replaced with a Sanyo CR2032, or equivalent, coin cell lithium battery. This battery has a 220 mAh rating.

#### CPU UPGRADE

A Type 7 Zero Insertion Force (ZIF) socket provides users with a performance upgrade path to the P54CTB OverDrive technology. LPX form factor makes it easier for the end user to replace the processor.

#### **GRAPHICS MEMORY UPGRADE**

The ATI-264VT graphics subsystem has either 1 or 2MB of SGRAM soldered down on the base board. Video memory can be upgraded with a daughter card that is compatible with ATI PCI add in cards. Information on the memory upgrade can be obtained by contacting ATI Technologies at the numbers listed below in the HARDWARE MPEG MODULE section.

# HARDWARE MPEG MODULE

ATI provides a hardware MPEG module that will work with the Advanced/RH. This module mounts onto connector J1H1, and uses mounting holes provided on the motherboard. This modul is also known as the ATI Multimedia Controller, or AMC.

For more information contact ATI Technologies at http://www.atitech.ca, or

(905) 882-2626 . . . . Customer Support (voice)

(905) 882-0546 . . . . Customer Support (fax)

(905) 764-9404 . . . . . ATI DOWNLOAD BBS (8N1)

# **Appendix B – Configuration Jumper Settings**

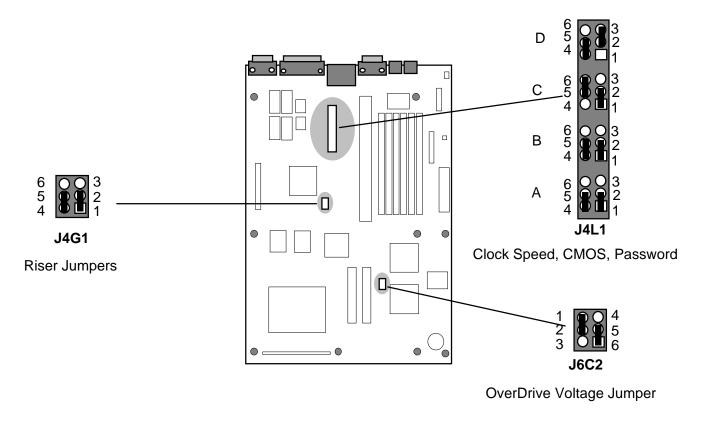

Figure B-1. Configuration Jumper locations

| FUNCTION                           | JUMPER<br>BLOCK | CONFIGURATION                        |

|------------------------------------|-----------------|--------------------------------------|

| FREQ **                            | BLOOK           | See table B-2 below                  |

| (Note: These jumpers also set PCI, | J4L1(C)         |                                      |

| and ISA clock speeds.)             | 0.11(0)         |                                      |

| MULT                               | J4L1(D)         | See table B-2 below                  |

| (cpu clock multiplier)             |                 |                                      |

| CMOS                               | J4L1(A)         | * 4-5 Keep (normal)                  |

| (resets CMOS settings to default)  |                 | 5-6 CLR (reset to default)           |

| PSWD                               | J4L1(A)         | * 1-2 Keep (Password Enabled)        |

| (Password Clear)                   |                 | 2-3 CLR (Password Clear/Disabled)    |

| SETUP                              | J4L1(B)         | * 1-2 ENBL (Access Allowed)          |

| (CMOS Setup Access)                | . ,             | 2-3 DIS (Access Denied)              |

| RISER                              | J4G1            | * 1-2 & 4-5 2 SLOTS                  |

| (Select # of PCI slots on riser)   |                 | 2-3 & 5-6 3 SLOTS                    |

| Recovery                           | J6C2            | *1-2 Normal operation                |

|                                    |                 | 2-3 Recovery mode                    |

| Drive or OverDrive                 | J6C2            | *5-6- Default voltage (VRE)          |

| Processor Voltage **               |                 | 4-5 OverDrive processor voltage (VR) |

\* Default configuration \*\* As shipped

Table B-1. Configuration Jumper settings

# CPU CONFIGURATION - JUMPER BLOCK J4L1(C&D)

These allow the motherboard to be switched between different speeds of the Pentium processor. These jumpers also affect the PCI and ISA clock speeds according to the following table:

| CPU Freq.<br>(MHz) | Host Bus<br>Freq. (MHz) | Host Bus<br>pins J4L1C<br>1-3 | Host Bus<br>pins J4L1C<br>4-6 | CLK Ratio | Clk Ratio<br>pins J4L1D<br>1-3 | Clk Ratio<br>pins J4L1D<br>4-6 | PCI Freq.<br>(MHz) |

|--------------------|-------------------------|-------------------------------|-------------------------------|-----------|--------------------------------|--------------------------------|--------------------|

| 166                | 66                      | 1-2                           | 5-6                           | 5/2       | 2-3                            | 5-6                            | 33                 |

| 150                | 60                      | 2-3                           | 4-5                           | 5/2       | 2-3                            | 5-6                            | 30                 |

| 133                | 66                      | 1-2                           | 5-6                           | 2         | 2-3                            | 4-5                            | 33                 |

| 120                | 60                      | 2-3                           | 4-5                           | 2         | 2-3                            | 4-5                            | 30                 |

| 100                | 66                      | 1-2                           | 5-6                           | 3/2       | 1-2                            | 4-5                            | 33                 |

| 90                 | 60                      | 2-3                           | 4-5                           | 3/2       | 1-2                            | 4-5                            | 30                 |

| 75                 | 50                      | 2-3                           | 5-6                           | 3/2       | 1-2                            | 4-5                            | 25                 |

| reserved           | -                       | 1-2                           | 4-5                           | -         | Х                              | Х                              | -                  |

Table B-2. CPU/SYSTEM speed settings (\* default setting)

The ISA clock is derived from the PCI bus clock. The BIOS automatically sets the ISA clock speed to one fourth of the PCI frequency.

| PCI Frequency | ISA clock speed |

|---------------|-----------------|

| 25 MHz        | 6.25 MHz        |

| 30 MHz        | 7.5 MHz         |

| 33 MHz        | 8.25 MHz        |

Table B-3. ISA clock settings set by the BIOS based on PCI Clk Speed

#### CMOS -J4L1 A PINS 4-6

Allows CMOS settings to be reset to default values by moving the jumper from pins 4-5 to pins 5-6 and turning the system on. When the system reports "NVRAM cleared by jumper", the system can be turned off and the jumper should be returned to the 4-5 position to restore normal operation. This procedure should be done whenever the system BIOS is updated. Default is for this jumper to be on pins 4-5.

#### PSWD -J4L1 A PINS 1-3

Allows system password to be cleared by moving the jumper from pins 1-2 to pins 2-3 and turning the system on. The system should then be turned off and the jumper should be returned to the 1-2 position to restore normal operation. This procedure should only be done if the user password has been forgotten. The password function is effectively disabled if this jumper is in the 2-3 position. Default is for the password to be enabled (1-2 position).

#### SETUP - J4L1 B PINS 1-3

Allows access to CMOS Setup utility to be disabled by moving this jumper from the 1-2 position to the 2-3 position. Default is for access to setup to be enabled (1-2 position).

#### RISER - J4G1

The riser jumper block allows routing of an extra IRQ and ID select to the riser card for an additional PCI slot to support a maximum of 3 PCI slots on a riser. Default is set for 2 PCI slots on the riser card (1-2 position and 4-5 position).

#### **DRIVE OR OVERDRIVE - J6C2**

Sets the CPU voltage to either standard voltage (3.3v), or OverDrive (3.6v). The Default setting is for a jumper to connect pin 5-6 for standard voltage. Move the jumper to connect pins 4-5 to select OverDrive voltage.

#### **RECOVERY JUMPER - J6C2**

This jumper should be set to normal mode, Pins 1-2, and should only be moved when a recovery is being performed, i.e. jumper 2-3.

# Appendix C – Memory Map

| Address Range | Address Range   | Size | Description                                       |  |

|---------------|-----------------|------|---------------------------------------------------|--|

| 1024K-512M    | 100000-20000000 | 511M | Extended Memory                                   |  |

| 960K-1023K    | F0000-FFFFF     | 64K  | AMI System run time BIOS                          |  |

| 944K-959K     | EC000-EFFFF     | 16K  | Main BIOS Recovery Code                           |  |

| 936K-943K     | EA000-EBFFF     | 8K   | ESCD (Plug 'N' Play configuration area)           |  |

| 928K-935K     | E8000-E9FFF     | 8K   | OEM LOGO (available as UMB)                       |  |

| 896K-927K     | E0000-E7FFF     | 32K  | BIOS RESERVED (Currently available as UMB)        |  |

| 800-895K      | C8000-DFFFF     | 96K  | Available HI DOS memory (open to ISA and PCI bus) |  |

| 640K-799K     | A0000-C7FFF     | 160K | Off-board video memory and BIOS                   |  |

| 639K          | 9FC00-9FFFF     | 1K   | Extended BIOS Data (moveable by QEMM, 386MAX)     |  |

| 512K-638K     | 80000-9FBFF     | 127K | Extended conventional                             |  |

| 0K-511K       | 00000-7FFFF     | 512K | Conventional                                      |  |

Table C-1. Advanced/RH Memory Map

The table above details the Advanced/RH memory map. The ESCD area from EA000-EBFFF is not available for use as an Upper Memory Block (UMB) by memory managers. The area from E0000-E7FFF is currently not used by the BIOS and is available for use as UMB by memory managers. Parts of this area may be used by future versions of the BIOS to add increased functionality.

# Appendix D – I/O Map

| Address (hex)  | Size     | Description             | Address (he)   | ) Size   | Description     |

|----------------|----------|-------------------------|----------------|----------|-----------------|

| 0000 - 000F    | 16 bytes | PIIX - DMA 1            | 0388 - 038B    | 4 bytes  |                 |

| 0020 - 0021    | 2 bytes  | PIIX - Interrupt        | 03B4 - 03B5    | 2 bytes  |                 |

| 002E - 002F    | 2 bytes  | Ultra I/O configuration | 03BA           | 1 byte   |                 |

| 0040 - 0043    | 4 bytes  | PIIX - Timer 1          | 03BC - 03BF    | 4 bytes  | Parallel Port 3 |

| 0048 - 004B    | 4 bytes  | PIIX - Timer 2          | 03C0 - 03CA    | 12 bytes |                 |

| 0060           | 1 byte   | Keyboard Controller     | 03CC           | 1 byte   |                 |

| 0061           | 1 byte   | PIIX - NMI, speaker     | 03CE - 03CF    | 2 bytes  |                 |

| 0064           | 1 byte   | Kbd Controller,         | 03D4 - 03D5    | 2 bytes  |                 |

| 0070, bit 7    | 1 bit    | PIIX - Enable NMI       | 03DA           | 1 byte   |                 |

| 0070, bits 6:0 | 7 bits   | PIIX - Real Time        | 03E8 - 03EF    | 8 bytes  | Serial Port 3   |

| 0071           | 1 byte   | PIIX - Real Time        | 03F0 - 03F5    | 6 bytes  | Floppy Channe   |

| 0078           | 1 byte   | Reserved - Brd.         | 03F6           | 1 byte   | Pri IDE Chan    |

| 0079           | 1 byte   | Reserved - Brd.         | 03F7 (Write)   | 1 byte   | Floppy Chan 1   |

| 0080 - 008F    | 16 bytes | PIIX - DMA Page         | 03F7, bit 7    | 1 bit    | Floppy Disk     |

| 00A0 - 00A1    | 2 bytes  | PIIX - Interrupt        | 03F7, bits 6:0 | 7 bits   | Pri IDE Chan    |

| 00C0 - 00DE    | 31 bytes | PIIX - DMA 2            | 03F8 - 03FF    | 8 bytes  | On-Board Ser    |

| 00F0           | 1 byte   | Reset Numeric Error     | LPT + 400h     | 8 bytes  | ECP port, LPT   |

| 0170 - 0177    | 8 bytes  | Secondary IDE           | 04D0 - 04D1    | 2 bytes  | Edge/Level      |

| 01F0 - 01F7    | 8 bytes  | Primary IDE Channel     | 0608 - 060B    | 4 bytes  |                 |

| 0200 - 0207    | 8 bytes  | Game Port               | 0CF8*          | 4 bytes  | PCI Config      |

| 0220 - 022F    | 8 bytes  |                         | 0CF9           | 1 byte   | Turbo & Rese    |

| 0278 - 027B    | 4 bytes  | Parallel Port 2         | 0CFC-0CFF      | 4 bytes  | PCI Config Da   |

| 02F8 - 02FF    | 8 bytes  | On-Board Serial Port 2  | 0FF0 - 0FF7    | 8 bytes  |                 |

| 0330 - 0331    | 1 bytes  | MPU - 401 (MIDI)        | FF00 - FF07    | 8 bytes  | IDE Bus Mast    |

| 0376           | 1 byte   | Sec IDE Chan Cmd        | FFA0 - FFA7    | 8 bytes  | IDE primary     |

| 0377           | 1 byte   | Sec IDE Chan Stat       | FFA8 - FFAF    | 8 bytes  | IDE secondar    |

| 0378 - 037F    | 8 bytes  | Parallel Port 1         |                |          |                 |

#### Table D-1. Advanced/RH I/O Address Map

I/O Port 78 is reserved for BIOS use. Port 79 is a read only port, the bit definitions are shown below in Table D-2.

| Bit # | Description                           | Bit = 1       | Bit = 0        |

|-------|---------------------------------------|---------------|----------------|

| 0     | Reserved                              | n/a           | n/a            |

| 1     | Soft Off capable power supply present | No            | Yes            |

| 2     | Onboard Audio present                 | Yes           | No             |

| 3     | External CPU clock                    | Table B-2     | Table B-2      |

| 4     | External CPU clock                    | Table B-2     | Table B-2      |

| 5     | Setup Disable                         | Enable access | Disable access |

| 6     | Clear CMOS                            | Keep values   | Clear values   |

| 7     | Password Clear                        | Keep password | Clear password |

Table D-2. Advanced/RH Port 79 Definition

# Appendix E – PCI Configuration Space Map

The 82430HX PCIset uses Configuration Mechanism 1 to access PCI configuration space. The PCI Configuration Address register is a 32-bit register located at CF8h, the PCI Configuration Data register is a 32-bit register located at CFCh. These registers are only accessible by full DWORD accesses. The table below lists the PCI bus and device numbers used by the motherboard.

| Bus Number | Dev Number (hex) | Func. Number | Description                                |

|------------|------------------|--------------|--------------------------------------------|

| 00         | 00               | 00           | Intel 82437HX                              |

| 00         | 07               | 00           | Intel 82371FB (PIIX 3) PCI/ISA bridge      |

| 00         | 07               | 01           | Intel 82371FB (PIIX 3) IDE Bus Master      |

| 00         | 08               | 00           | Video [ATI]                                |

| 00         | 0B               | 00           | Option PCI expansion Slot for 3 Slot Riser |

| 00         | 11               | 00           | PCI Expansion Slot                         |

| 00         | 13               | 00           | PCI Expansion Slot                         |

Table E-1. Advanced/RH PCI Configuration. Space Map

# Appendix F – Interrupts & DMA Channels

| IRQSystem ResourceNMII/O Channel Check0Reserved, Interval Timer1Reserved, Keyboard buffer full2Reserved, Cascade interrupt from slave PIC3Serial Port 24Serial Port 15Audio6Floppy7Parallel Port 18Real Time Clock9User available10User available11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE      |     |                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------|

| 0Reserved, Interval Timer1Reserved, Keyboard buffer full2Reserved, Cascade interrupt from slave PIC3Serial Port 24Serial Port 15Audio6Floppy7Parallel Port 18Real Time Clock9User available10User available11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                            | IRQ | System Resource                               |

| 1Reserved, Keyboard buffer full2Reserved, Cascade interrupt from slave PIC3Serial Port 24Serial Port 15Audio6Floppy7Parallel Port 18Real Time Clock9User available10User available11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                                                     | NMI | I/O Channel Check                             |

| 2Reserved, Cascade interrupt from slave PIC3Serial Port 24Serial Port 15Audio6Floppy7Parallel Port 18Real Time Clock9User available10User available11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                                                                                    | 0   | Reserved, Interval Timer                      |

| <ul> <li>3 Serial Port 2</li> <li>4 Serial Port 1</li> <li>5 Audio</li> <li>6 Floppy</li> <li>7 Parallel Port 1</li> <li>8 Real Time Clock</li> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul> | 1   | Reserved, Keyboard buffer full                |

| <ul> <li>4 Serial Port 1</li> <li>5 Audio</li> <li>6 Floppy</li> <li>7 Parallel Port 1</li> <li>8 Real Time Clock</li> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul>                          | 2   | Reserved, Cascade interrupt from slave PIC    |

| <ul> <li>5 Audio</li> <li>6 Floppy</li> <li>7 Parallel Port 1</li> <li>8 Real Time Clock</li> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul>                                                   | 3   | Serial Port 2                                 |

| <ul> <li>Floppy</li> <li>Parallel Port 1</li> <li>Real Time Clock</li> <li>User available</li> <li>User available</li> <li>User available</li> <li>Onboard Mouse Port</li> <li>Reserved, Math coprocessor</li> <li>Primary IDE</li> </ul>                                                                                  | 4   | Serial Port 1                                 |

| <ul> <li>7 Parallel Port 1</li> <li>8 Real Time Clock</li> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul>                                                                                      | 5   | Audio                                         |

| <ul> <li>8 Real Time Clock</li> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul>                                                                                                                 | 6   | Floppy                                        |

| <ul> <li>9 User available</li> <li>10 User available</li> <li>11 Audio</li> <li>12 Onboard Mouse Port</li> <li>13 Reserved, Math coprocessor</li> <li>14 Primary IDE</li> </ul>                                                                                                                                            | 7   | Parallel Port 1                               |

| 10User available11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                                                                                                                                                                                                                       | 8   | Real Time Clock                               |

| 11Audio12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                                                                                                                                                                                                                                       | 9   | User available                                |

| 12Onboard Mouse Port13Reserved, Math coprocessor14Primary IDE                                                                                                                                                                                                                                                              | 10  | User available                                |

| 13Reserved, Math coprocessor14Primary IDE                                                                                                                                                                                                                                                                                  | 11  | Audio                                         |

| 14 Primary IDE                                                                                                                                                                                                                                                                                                             | 12  | Onboard Mouse Port                            |

|                                                                                                                                                                                                                                                                                                                            | 13  | Reserved, Math coprocessor                    |

|                                                                                                                                                                                                                                                                                                                            | 14  | Primary IDE                                   |

| 15 Secondary IDE if present, else user available                                                                                                                                                                                                                                                                           | 15  | Secondary IDE if present, else user available |

| DMA | Data Width    | System Resource                     |

|-----|---------------|-------------------------------------|

| 0   | 8- or 16-bits | Audio                               |

| 1   | 8- or 16-bits | Audio                               |

| 2   | 8- or 16-bits | Floppy                              |

| 3   | 8- or 16-bits | Parallel Port (for ECP/EPP Config.) |

| 4   |               | Reserved - Cascade channel          |

| 5   | 16-bits       | Open                                |

| 6   | 16-bits       | Open                                |

| 7   | 16-bits       | Open                                |

Table F-2. Advanced/RH DMA Map

Table F-1. Advanced/RH Interrupts

# Appendix G – Connectors

# POWER SUPPLY

#### PRIMARY POWER J9H1

| Pin | Name                                                  | Function                                                                                                                                                                                                                                                                  |

|-----|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PWRGD                                                 | Power Good                                                                                                                                                                                                                                                                |

| 2   | +5 V                                                  | + 5 volts Vcc                                                                                                                                                                                                                                                             |

| 3   | +12 V                                                 | + 12 volts                                                                                                                                                                                                                                                                |

| 4   | -12 V                                                 | - 12 volts                                                                                                                                                                                                                                                                |

| 5   | GND                                                   | Ground                                                                                                                                                                                                                                                                    |

| 6   | GND                                                   | Ground                                                                                                                                                                                                                                                                    |

| 7   | GND                                                   | Ground                                                                                                                                                                                                                                                                    |

| 8   | GND                                                   | Ground                                                                                                                                                                                                                                                                    |

| 9   | -5 V                                                  | -5 volts                                                                                                                                                                                                                                                                  |

| 10  | +5 V                                                  | + 5 volts Vcc                                                                                                                                                                                                                                                             |

| 11  | +5 V                                                  | + 5 volts Vcc                                                                                                                                                                                                                                                             |

| 12  | +5 V                                                  | + 5 volts Vcc                                                                                                                                                                                                                                                             |

|     | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | 1         PWRGD           2         +5 V           3         +12 V           4         -12 V           5         GND           6         GND           7         GND           8         GND           9         -5 V           10         +5 V           11         +5 V |

# PCI (3.3V) POWER J9J1 NOT POPULATED

| Pin | Name   | Function    |

|-----|--------|-------------|

| 1   | GND    | Ground      |

| 2   | GND    | Ground      |

| 3   | GND    | Ground      |

| 4   | +3.3 V | + 3.3 volts |

| 5   | +3.3V  | + 3.3 volts |

| 6   | +3.3 V | + 3.3 volts |

#### FRONT PANEL-J3A1

#### SLEEP/RESUME

| Pin | Signal Name |  |

|-----|-------------|--|

| 15  | SW_ON       |  |

| 16  | GND         |  |

| 17  | SLEEP       |  |

| 18  | SLEEPPU     |  |

| 19  | KEY         |  |

#### INFRA-RED

| Pin | Signal Name |  |

|-----|-------------|--|

| 25  | CONIRRX     |  |

| 24  | IRTX        |  |

| 23  | GND         |  |

| 22  | IRRIN       |  |

| 21  | NC          |  |

| 20  | VCC         |  |

#### POWER INTERFACE CPU FAN

|    | Signal Name |

|----|-------------|

| 3  | Ground      |

| 2  | +12V        |

| 31 | Ground      |

#### POWER INTERFACE SPEAKER CONNECTOR

| Pin | Signal Name |  |

|-----|-------------|--|

| 29  | GND         |  |

| 28  | Key         |  |

| 27  | SPKSRC      |  |

| 26  | SPKOUT      |  |

#### POWER INTERFACE HARD DRIVE LED (DISK)

| Pin | Signal Name |

|-----|-------------|

| 14  | PWRPU       |

| 13  | PWDRV       |

| 12  | HDA         |

| 11  | HDPU        |

# POWER LED / KEYLOCK

|    | Signal Name |

|----|-------------|

| 10 | PWDRV       |

| 9  | NC          |

| 8  | PWRPU       |

| 7  | KEY         |

#### POWER INTERFACE RESET CONNECTOR

| ^ |                |        |  |  |  |  |

|---|----------------|--------|--|--|--|--|

|   | Pin Signal Nar |        |  |  |  |  |

|   | 6              | Key    |  |  |  |  |

|   | 5              | RESET  |  |  |  |  |

|   | 4              | Ground |  |  |  |  |

### BACK PANEL I/O

PS/2 KEYBOARD J8N1 & MOUSE PORTS J7N1

| Pin | Signal Name |  |  |  |

|-----|-------------|--|--|--|

| 1   | Data        |  |  |  |

| 2   | No Connect  |  |  |  |

| 3   | Ground      |  |  |  |

| 4   | Vcc         |  |  |  |

| 5   | Clock       |  |  |  |

# SERIAL PORTS COM1 J6N2 & COM2

J5N1

| ••              |                     |  |  |  |  |

|-----------------|---------------------|--|--|--|--|

| Pin Signal Name |                     |  |  |  |  |

| 1               | DCD                 |  |  |  |  |

| 2               | Serial In - (SIN)   |  |  |  |  |

| 3               | Serial Out - (SOUT) |  |  |  |  |

| 4               | DTR-                |  |  |  |  |

| 5               | GND                 |  |  |  |  |

| 6               | DSR-                |  |  |  |  |

| 7               | RTS-                |  |  |  |  |

| 8               | CTS-                |  |  |  |  |

| 9               | RI                  |  |  |  |  |

# US<u>B J5N2 REPLACES</u>COM2

| Pin | Signal Name |  |  |  |  |  |

|-----|-------------|--|--|--|--|--|

| 1   | VCC         |  |  |  |  |  |

| 2   | USBP0-      |  |  |  |  |  |

| 3   | USBP0       |  |  |  |  |  |

| 4   | GND         |  |  |  |  |  |

| 5   | VCC         |  |  |  |  |  |

| 6   | USBP1-      |  |  |  |  |  |

| 7   | USBP1       |  |  |  |  |  |

| 8   | GND         |  |  |  |  |  |

#### LINE OUT J9N2

| Pin | Signal Name |  |  |  |

|-----|-------------|--|--|--|

| 1   | Line Out    |  |  |  |

### MIC IN J8N2

| Pin | Signal Name |

|-----|-------------|

| 1   | Line Out    |

#### PARALLEL PORT J3N1

| Signal Name    | Pin | Pin | Signal Name |

|----------------|-----|-----|-------------|

| STROBE-        | 1   | 14  | AUTO FEED-  |

| Data Bit 0     | 2   | 15  | ERROR-      |

| Data Bit 1     | 3   | 16  | INIT-       |

| Data Bit 2     | 4   | 17  | SLCT IN-    |

| Data Bit 3     | 5   | 18  | Ground      |

| Data Bit 4     | 6   | 19  | Ground      |

| Data Bit 5     | 7   | 20  | Ground      |

| Data Bit 6     | 8   | 21  | Ground      |

| Data Bit 7     | 9   | 22  | Ground      |

| ACK-           | 10  | 23  | Ground      |

| BUSY           | 11  | 24  | Ground      |

| PE (Paper End) | 12  | 25  | Ground      |

| SLCT           | 13  | 26  | N.C.        |

# VIDEO MONITOR PORT J1N1

| Pin | Signal Name      |  |  |  |

|-----|------------------|--|--|--|

| 1   | Red              |  |  |  |

| 2   | Green            |  |  |  |

| 3   | Blue             |  |  |  |

| 4   | No Connect       |  |  |  |

| 5   | Ground           |  |  |  |

| 6   | Ground           |  |  |  |

| 7   | Ground           |  |  |  |

| 8   | Ground           |  |  |  |

| 9   | No Connect       |  |  |  |

| 10  | Ground           |  |  |  |

| 11  | No Connect       |  |  |  |

| 12  | MONID1           |  |  |  |

| 13  | Horizontal Sync. |  |  |  |

| 14  | Vertical Sync.   |  |  |  |

| 15  | MONID2           |  |  |  |

# PERIPHERALS

| IDE CONNECTORS | J5C1 | & J6C1 |

|----------------|------|--------|

|----------------|------|--------|

| Signal Name          | Pin | Pin | Signal Name          |  |  |  |

|----------------------|-----|-----|----------------------|--|--|--|

| Reset IDE            | 1   | 2   | Ground               |  |  |  |

| Host Data 7          | 3   | 4   | Host Data 8          |  |  |  |

| Host Data 6          | 5   | 6   | Host Data 9          |  |  |  |

| Host Data 5          | 7   | 8   | Host Data 10         |  |  |  |

| Host Data 4          | 9   | 10  | Host Data 11         |  |  |  |

| Host Data 3          | 11  | 12  | Host Data 12         |  |  |  |